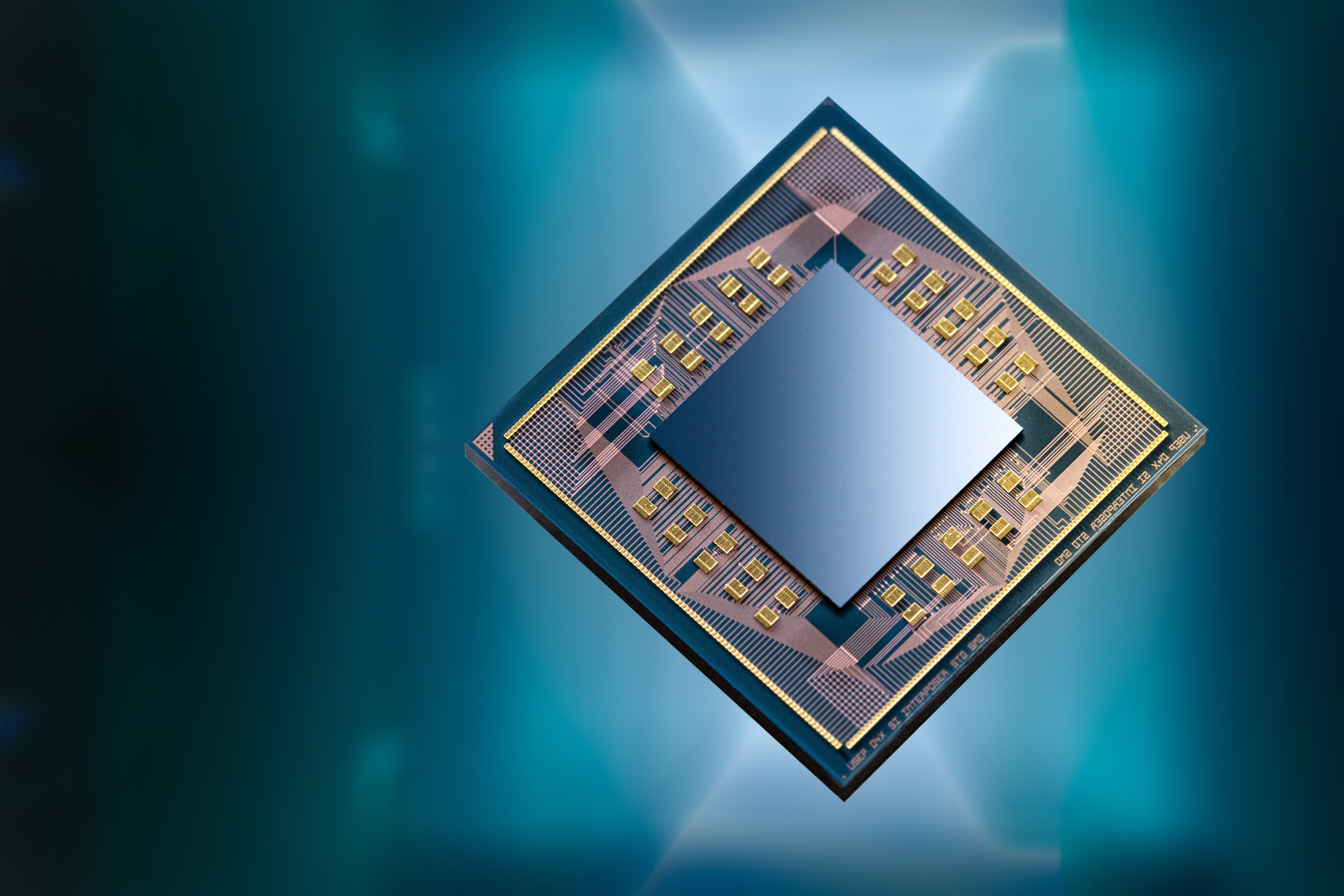

From design and frontend to backend and system integration

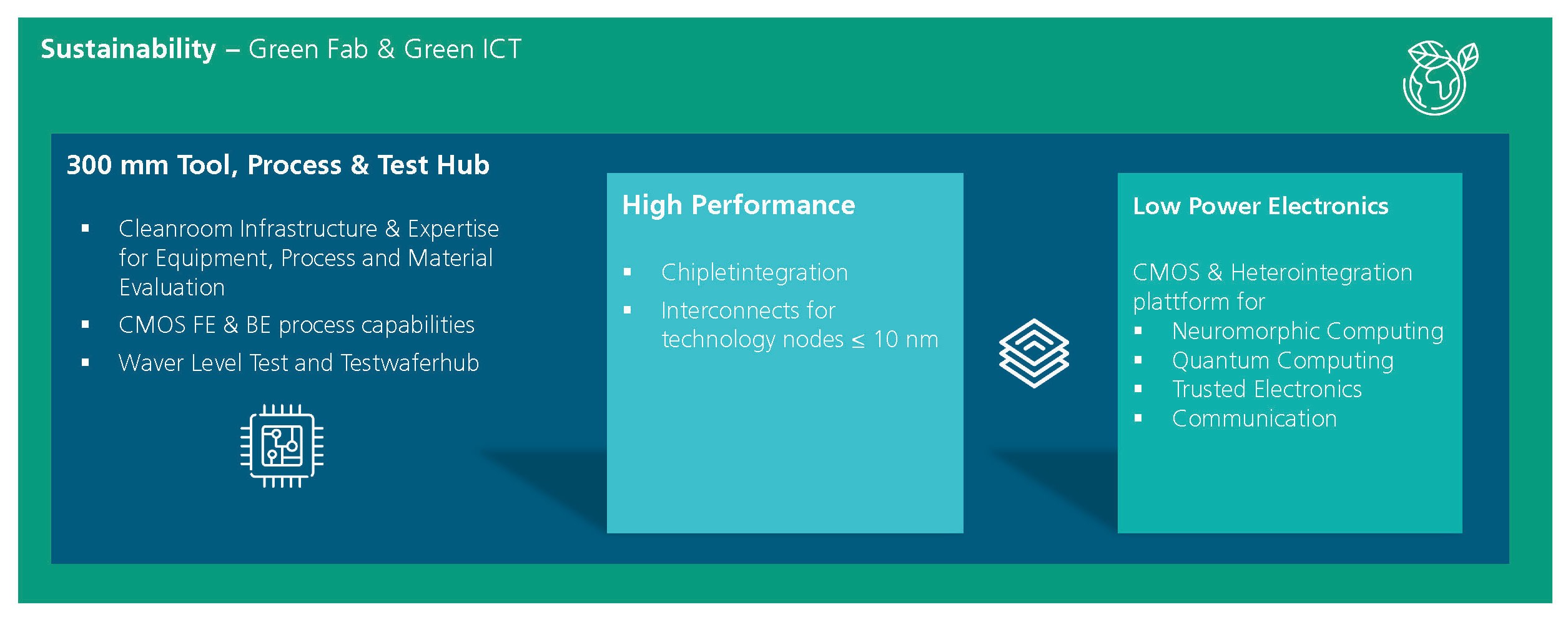

We offer you 300 mm CMOS process and device development with front-end integration as well as 300 mm heterogeneous wafer-level system integration.

Processes

- Atomic Layer Deposition (ALD)

- Nanopatterning / E-Beam Lithography

- Chemical Mechanical Polishing (CMP)

- Wafer Metallization

- Wafer Cleaning

- Wafer Services

- 2.5/3D Technologies

- High Density Redistribution

- Wafer bumping

- Wafer bonding

- Thinning/Singulation/Dicing

- High-Density Assembly

- Failure Analysis & Reliability Investigation

- Sensor Development

- Photonic & Plasmonic Systems

Systems

- 3D wafer-level system-in-package WL SiP, CSP

- Application-specific Cu-TSV integration: via middle, via last, backside TSV

- Si-interposer with TSV, multi-layer RDL, micro-cavities and integrated passives

- Glass interposer w/wo TGV, multi-layer RDL and µ-interconnects

- High-density, multi-pitch and size micro-bump or pillar interconnect formation

- Temporary and permanent wafer bonding (adhesive, soldering, direct)

- Hybrid Bonding, Direct bond interconnects (DBI) – W2W, D2

- BEoL Cu-interconnects compatible to 28/22 FDX technology nodes

Integration

- Integration of

- Non-volatile memories: STT-/SOT-MRAM / Racetrack, RRAM, FeFet, FRAM

- Spin-based and superconducting qubits

- Micromagnets and superconducting wiring

- High-capacitance capacitors and resistor networks

- Integrable sensor systems (thermopiles, IR detectors)

Center for Advanced CMOS & Heterointegration Saxony

Center for Advanced CMOS & Heterointegration Saxony